# Datasheet for Chipsemi CHSC6440

DS-CHSC6440

Ver 1.2.0

## **Keyword:**

Features; Benefits; Operation modes; CDSP; MCU; Clock; Timer; Watchdog; Interface; Interrupt; Memory; ADC; Electrical specifications; Applications.

#### **Brief:**

This datasheet is dedicated for the self-capacitive touch panel controller IC CHSC6440 developed by Chipsemi. In this datasheet, key features, operation mode, main modules and reference design of the CHSC6440 are introduced.

Published by Chipsemi(Ning Bo) Co., Ltd.

475 Ye Shan RD, Yu Yao Zhejiang , China

© Chipsemi Semiconductor All Right Reserved

#### **Legal Disclaimer**

Chipsemi(Ning Bo) Co., Ltd. (Chipsemi) reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Chipsemi disclaims any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Chipsemi does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications. Customers using or selling Chipsemi products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Chipsemi for any damages arising or resulting from such use or sale.

## Information:

For further information on the technology, product and business term, please contact Chipsemi Company (<a href="https://www.Chipsemicorp.com">www.Chipsemicorp.com</a>).

For sales or technical support, please send email to the address of:

sales@chipsemicorp.com

support@chipsemicorp.com

DS-CHSC6440 1 Ver 1.2.0

## **Revision History**

| Version | Major Changes                                                                               | Date    | Author          |

|---------|---------------------------------------------------------------------------------------------|---------|-----------------|

| 1.0.0   | Initial release                                                                             | 2016/11 | X.S.J., Cynthia |

| 1.2.0   | Added CHSC6440EU48 package information.  Updated package dimension figure for CHSC6440EU48. | 2017/12 | B. Xia          |

|         |                                                                                             |         |                 |

|         |                                                                                             |         |                 |

|         |                                                                                             |         |                 |

|         |                                                                                             |         |                 |

|         |                                                                                             |         |                 |

|         |                                                                                             |         |                 |

DS-CHSC6440 2 Ver 1.2.0

## 1 Table of contents

| 1 | Intr | odu   | ction                               | . 7 |

|---|------|-------|-------------------------------------|-----|

|   | 1.1  | Ge    | eneral description                  | .7  |

|   | 1.2  | Ke    | y features                          | .7  |

|   | 1.3  | Key   | benefits                            | .8  |

|   | 1.4  | Тур   | ical application                    | .9  |

|   | 1.5  | Ord   | ering information                   | 10  |

|   | 1.6  | Pac   | kage                                | 10  |

|   | 1.7  |       | layout                              |     |

| 2 | Fun  | ctio  | n Overview                          | 14  |

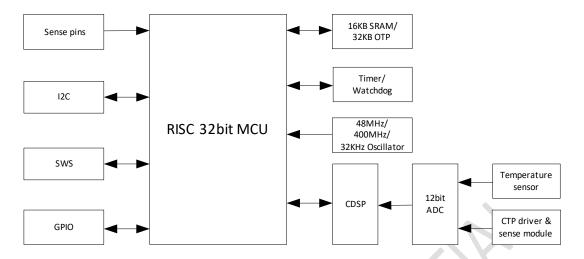

|   | 2.1  | Bloc  | ck diagram                          |     |

|   | 2.1. | 1     | Memory                              |     |

|   | 2.1. | 2     | Interface                           |     |

|   | 2.1. | 3     | Digital part                        |     |

|   | 2.1. | 4     | Analog part                         | 15  |

|   | 2.2  | СТР   | operation modes                     | 16  |

|   | 2.2. | 1     | Normal mode                         |     |

|   | 2.2. | 2     | Low-power mode                      | 16  |

|   | 2.2. |       | Suspend mode                        |     |

| 3 |      |       |                                     |     |

| 4 | MC   | U     |                                     | 17  |

|   | 4.1  | De    | escription                          | 17  |

|   | 4.2  | Clo   | ock                                 | 17  |

|   | 4.2. | 1     | System clock                        | 17  |

|   | 4.2. | 2     | ADC clock                           | 18  |

|   | 4.3  | Re    | set, Wakeup and Power down enabling | 18  |

| 5 | Tim  | ers.  |                                     | 18  |

|   | 5.1  | Мо    | de0 (System Clock Mode)             | 18  |

|   | 5.2  | Мо    | de1 (GPIO Trigger Mode)             | 18  |

|   | 5.3  | Мо    | de2 (GPIO Pulse Width Mode)         | 19  |

|   | 5.4  | Мо    | de3 (Tick Mode)                     | 19  |

|   | 5.5  | No-   | wrap mode                           | 19  |

|   | 5.6  | Wat   | tchdog                              | 20  |

| 6 | Inte | erfac | e                                   | 21  |

|   | 6.1  | I2C   |                                     | 22  |

| 7 | Inte  | errupt system                         | 23 |

|---|-------|---------------------------------------|----|

|   | 7.1   | Enable interrupt sources and priority | 23 |

|   | 7.2   | Interrupt source indication           | 23 |

|   | 7.3   | Clear IRQ source                      | 23 |

| 8 | Me    | mory configuration                    | 24 |

| 9 | SAF   | R ADC                                 | 24 |

|   | 9.1   | Clock                                 | 24 |

|   | 9.2   | Resolution                            | 24 |

|   | 9.3   | Reference voltage and sampling period |    |

|   | 9.4   | Input mode and channel selection      | 25 |

|   | 9.6   | Reset and power down                  | 25 |

| 1 | 0 Key | Electrical Specifications             | 25 |

|   | 10.1  | Absolute maximum ratings              | 25 |

|   |       | Recommended operating condition       | 26 |

|   | 10.3  | DC characteristics                    | 27 |

|   | 10.4  | AC characteristics                    | 27 |

## 2 Table of Figures

| Figure 1- 1 Pack  | age dimension for the CHSC6440EU48                  | 12   |

|-------------------|-----------------------------------------------------|------|

| Figure 1- 2 Pin a | ssignment for the CHSC6440                          | . 13 |

|                   |                                                     |      |

| Fig. 2. 4         | Disability and                                      | 4.5  |

| Figure 2- 1       | BIOCK diagram                                       | 15   |

|                   |                                                     |      |

| Figure 6- 1       | Schematic diagram for interface                     | 21   |

| Figure 6- 2       | Connection schematic between I2C and AIF_CTL module | 22   |

DS-CHSC6440 5 Ver 1.2.0

## 3 Table of Tables

| Table 1- 1  | Key features of CHSC6440             |    |

|-------------|--------------------------------------|----|

| Table 1-2   | Ordering information of the CHSC6440 | 10 |

| Table 1-3   | Pin functions for the CHSC6440       | 13 |

|             |                                      |    |

| Table 10- 1 | Absolute Maximum Ratings             | 25 |

| Table 10- 2 | Recommended operation condition      | 26 |

| Table 10- 3 | DC characteristics                   | 27 |

|             |                                      |    |

| Table 10- 4 | AC Characteristics                   | 27 |

#### 1 Introduction

## 1.1 General description

CHSC6440, latest generation single-chip self-capacitive touch panel controller SoC developed by Chipsemi, is designed to work with self-capacitance type sensor, and supports user-friendly gesture control and up to two-point touch with a capacitive touch panel. Single-chip CHSC6440 supports up to 7" touch panel.

With built-in 32-bit RISC processor and CDSP module, the CHSC6440 is featured with outstanding noise immunity, fast response, low power consumption, excellent accuracy and linearity, as well as perfect waterproof performance.

CHSC6440, which operates in the -40  $^{\circ}$ C  $^{\sim}$ +125  $^{\circ}$ C industrial temperature range, can be applied to a diverse group of portable devices, such as cellular phones, tablets, and GPS navigator.

CHSC6440 offers high-volume-assembly and high integration level. Few external components are needed to satisfy customers' ultra-low cost requirement. It's completely RoHS-compliant and 100% lead (Pb)-free.

## 1.2 Key features

Table 1-1 Key features of CHSC6440

| Features         | CHSC6440                                                   |  |  |  |  |  |

|------------------|------------------------------------------------------------|--|--|--|--|--|

| Package          | UQFN-48, 5X5X0.55mm                                        |  |  |  |  |  |

|                  | G/G, G/F, P/F, OGS, Ultra-thin G/F                         |  |  |  |  |  |

| Touch sensor     | (Support ITO traces; support direct bonding; support       |  |  |  |  |  |

|                  | frameless TP)                                              |  |  |  |  |  |

| ITO pattern      | single layer self-capacitance                              |  |  |  |  |  |

| Touch panel size | 4.3"~7"                                                    |  |  |  |  |  |

|                  | Power-on time: <75ms; Latency time for first touch: <12ms. |  |  |  |  |  |

| Response time    | Scanning speed: up to 200Hz                                |  |  |  |  |  |

DS-CHSC6440 7 Ver 1.2.0

| Features                             | CHSC6440                                                                               |  |  |

|--------------------------------------|----------------------------------------------------------------------------------------|--|--|

| Operating voltage                    | 2.6V~3.6V                                                                              |  |  |

| Operating temperature                | -40°C~+125°C                                                                           |  |  |

| Supported channel number             | 40                                                                                     |  |  |

| Supported channel driving resistance | <100kΩ                                                                                 |  |  |

| Supported single channel capacitance | Up to 400pF                                                                            |  |  |

| Power consumption                    | Current-active: 8mA (Typ), Current-sleep: 7uA (Typ), I/O Latch-up current: 200mA (min) |  |  |

| ESD                                  | HBM 6000V (min.), MM 300V (min.), CDM 500V (min.), Air Discharge +/-10 kV (min.)       |  |  |

| Multi-point touch                    | Up to 2 points                                                                         |  |  |

| Glove mode                           | Support                                                                                |  |  |

| Anti-interference performance        | Immune to noise from RF, LCD and power supply                                          |  |  |

## 1.3 Key benefits

(1) Anti-Interference and excellent noise-cancellation performance:

Immune to RF interferences, robust operation in noisy RF environment;

Insensitive to capacitance and environmental variety via auto calibration function;

Chipsemi's innovative adaptive-noise-cancellation technology and specially designed data processing unit can detect and silence the two noise sources which capacitive touch screen usually suffers from: display noise and charger noise. With the powerful 32bit MCU and specific built-in hardware, both the periodic and broadband noise can be eliminated to obtain unmatched noise immunity.

(2) Fast response time:

DS-CHSC6440 8 Ver 1.2.0

The power-on time for the CHSC6440 is less than 75ms;

When it is powered up, the latency time for first touch is less than 12ms;

Scanning rate up to 200Hz makes fast response available, which is especially useful for the highly demanding applications for the responding speed, such as handwriting and game.

#### (3) Low power consumption:

The average current in typical case is 8mA at active state, and 7uA in suspend mode.

#### (4) Excellent waterproof performance:

Water mist even droplets on the surface will not influence normal operation of touch panel based on the CHSC6440.

When water mist or droplets are wiped off, the touch screen can also be operated normally without extra delays.

No malfunction or dummy points will be reported during water spurting and wiping process.

#### 1.4 Typical application

The CHSC6440 is dedicated for self-capacitive touch panel; its typical applications are listed as follows:

- ♦ Smart phone

- ♦ Tablets

- ♦ Digital camera

- ♦ GPS navigator

- ♦ Portable media player

- ♦ Game consoles.

DS-CHSC6440 9 Ver 1.2.0

## 1.5 Ordering information

Table 1-2

Order

## ing information of the CHSC6440

| Product<br>Series | Package Type | Temperature<br>Range | Product Part<br>No. | Packing<br>Method | Ordering<br>Number | Minimum<br>Order Quantity |

|-------------------|--------------|----------------------|---------------------|-------------------|--------------------|---------------------------|

|                   | 48-pin       | -40°C~+125°C         |                     |                   |                    |                           |

| CHSC6440          | 5x5x0.55mm   | -40 C*+125 C         | CHSC6440EU48        | TR                | CHSC6440EU48R      | 3000                      |

|                   | UQFN         |                      |                     |                   |                    |                           |

<sup>\*</sup>Note: Packing method "TR" means tape and reel.

## 1.6 Package

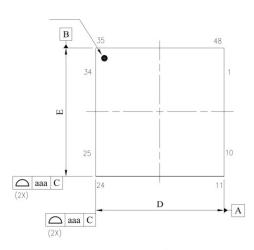

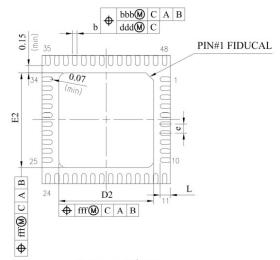

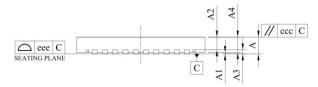

Package dimension for the CHSC6440EU48 is shown as Figure 1-1.

DS-CHSC6440 10 Ver 1.2.0

Top View

Bottom View

Side View

| ITEM                      |              | Symbol | DIMENSION(mm) |         |      |  |

|---------------------------|--------------|--------|---------------|---------|------|--|

| HEM                       | Symbol       | MIN.   | NOM.          | MAX.    |      |  |

| Total height              | Total height |        |               | 0.55    | 0.60 |  |

| Stand off                 |              | A1     | 0             | 0.02    | 0.05 |  |

| Mold thickness            |              | A2     | 0.38          | 0.40    | 0.41 |  |

| Leadframe thickness       |              | A3     |               | 0.15REF |      |  |

| Mold+Leadframe thickness+ | Mold gap     | A4     | 0.50          | 0.53    | 0.60 |  |

| Lead width                |              | b      | 0.13          | 0.18    | 0.23 |  |

| Package size              | X            | D      | 4.90          | 5.00    | 5.10 |  |

| rackage size              | Y            | Е      | 4.90          | 5.00    | 5.10 |  |

| E-PAD Size                | X            | D2     | 3.60          | 3.70    | 3.80 |  |

| L-I AD SIZE               | Y            | E2     | 3.60          | 3.70    | 3.80 |  |

| Lead length               |              | L      | 0.35          | 0.40    | 0.45 |  |

| Lead pitch                |              | e      | 0.25          | 0.35    | 0.45 |  |

| Package profile of a s    | urface       | aaa    | 0.10          |         |      |  |

| Lead position             |              | bbb    | 0.07          |         |      |  |

| Paralleliam               | ccc          | 0.10   |               |         |      |  |

| Lead position             | ddd          | 0.05   |               |         |      |  |

| Package profile of a s    | urface       | eee    | 0.08          |         |      |  |

| Epad position             |              | fff    | 0.10          |         |      |  |

- 1. DIMENSIONING AND TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. REFER TO JEDEC STD.MO-220 WJJE-1.

3. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25mm FROM TERMINAL TIP.

4. LEADFRAME MATERIAL IS 194FH AND THICKNESS IS 0.203MM (8 MIL).

- 5. DIMENSION"D"&"E" WILL INCLUDE ALL SIDE BURR INDUCED DURING ASSEMBLY.

Figure 1-1 Package dimension for the CHSC6440EU48

DS-CHSC6440 12 Ver 1.2.0

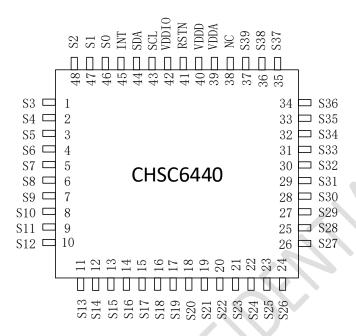

## 1.7 Pin layout

Figure 1-2 Pin assignment for the CHSC6440

Functions of 48 pins for the CHSC6440 (CHSC6440EU48) are described in Table 1-3

Table 1-3 Pin functions for the CHSC6440

| Pin No. | Type                                                                                      | Description                             |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| 1       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 2       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 3       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 4       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 5       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 6       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 7       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 8       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 9       | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 10      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 11      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 12      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 13      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 14      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 15      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 16      | Ι                                                                                         | sense input                             |  |  |  |  |  |  |

| 17      | I                                                                                         | sense input                             |  |  |  |  |  |  |

| 18      | I                                                                                         | sense input                             |  |  |  |  |  |  |

|         | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17 | 1 I I I I I I I I I I I I I I I I I I I |  |  |  |  |  |  |

DS-CHSC6440 13 Ver 1.2.0

| Pin Name | Pin No. | Type | Description                                                           |  |  |

|----------|---------|------|-----------------------------------------------------------------------|--|--|

| S21      | 19      | I    | sense input                                                           |  |  |

| S22      | 20      | I    | sense input                                                           |  |  |

| S23      | 21      | I    | sense input                                                           |  |  |

| S24      | 22      | I    | sense input                                                           |  |  |

| S25      | 23      | I    | sense input                                                           |  |  |

| S26      | 24      | Ι    | sense input                                                           |  |  |

| S27      | 25      | Ι    | sense input                                                           |  |  |

| S28      | 26      | I    | sense input                                                           |  |  |

| S29      | 27      | I    | sense input                                                           |  |  |

| S30      | 28      | I    | sense input                                                           |  |  |

| S31      | 29      | I    | sense input                                                           |  |  |

| S32      | 30      | I    | sense input                                                           |  |  |

| S33      | 31      | I    | sense input                                                           |  |  |

| S34      | 32      | I    | sense input                                                           |  |  |

| S35      | 33      | I    | sense input                                                           |  |  |

| S36      | 34      | I    | sense input                                                           |  |  |

| S37      | 35      | I    | sense input                                                           |  |  |

| S38      | 36      | I    | sense input                                                           |  |  |

| S39      | 37      | I    | sense input                                                           |  |  |

| NC       | 38      | NC   | no connection                                                         |  |  |

| VDDA     | 39      | PWR  | Analog power supply, A 1 µ F ceramic capacitor to ground is required. |  |  |

| VDDD     | 40      | PWR  | Digital power supply, 1uF capacitor to ground is required.            |  |  |

| RSTN     | 41      | I    | Capacitor to ground is required.                                      |  |  |

| VDDIO    | 42      | PWR  | I/O power supply                                                      |  |  |

| SCL      | 43      | I/0  | I2C clock input                                                       |  |  |

| SDA      | 44      | I/0  | I2C data input and output                                             |  |  |

| INT      | 45      | I/0  | External interrupt to the host                                        |  |  |

| S0       | 46      | Ι    | sense input                                                           |  |  |

| S1       | 47      | Ι    | sense input                                                           |  |  |

| S2       | 48      | Ι    | sense input                                                           |  |  |

<sup>\*</sup>Note: Pins with bold typeface can be used as GPIOs.

## **2** Function Overview

## 2.1 Block diagram

The overall system block diagram of the CHSC6440 is shown as Figure 2-1.

DS-CHSC6440 14 Ver 1.2.0

Figure 2-1 Block diagram

#### 2.1.1 Memory

- ♦ 128KB Flash;

- ♦ SRAM: 8KB SRAM for system use; 2KB SRAM for CDSP use;

#### 2.1.2 Interface

♦ CHSC6440: 40 CTP sense pins; GPIO/I2C/SWS.

#### 2.1.3 Digital part

- ♦ A 32-bit RISC processor with a 32×32 multiplier and a 32/32 divider;

- ♦ Embeds CDSP module to obtain accurate coordinate of touch points via firmware; the CDSP supports totally up to 40 sensing lines for the CHSC6440;

- Timer: Integrates 3 timers and there are four modes available for each timer;

Timer2 can be configured as a watchdog so as to reset chip from unexpected hang up or malfunction.

#### 2.1.4 Analog part

CTP driver & sense module: The sensing circuit adopts the patented charger fast detection technology for efficiency.

DS-CHSC6440 15 Ver 1.2.0

- ♦ Embeds a temperature sensor which serves to measure ambient environment temperature so as to implement temperature compensation via firmware.

- ❖ ADC: The 12-bit ADC serves to take samples of temperature sensor/integrator output, conduct analog-to-digital signal conversion, and send digital signal after conversion to the CDSP module.

- ♦ Clock: Embeds a 48MHz RC oscillator and a 400MHZ RC oscillator.

- ♦ DCDC: Embeds a step-up DCDC to convert 3.3V input into 6.75V output. It serves to provide power for internal OTP writing.

- ❖ Regulator: Embeds a LDO (Low Dropout) regulator to provide power for internal clock. Also embeds a DIG\_LDO and a LC\_LDO to provide power for digital parts in normal working mode and low current mode, respectively.

- ♦ Bandgap: Provides voltage reference value.

- → Embeds a 32KHz RC oscillator which serves to generate a clock for suspend mode wakeup.

## 2.2 CTP operation modes

For the CHSC6440, there are three operation modes available as follows: normal mode, low-power mode and suspend mode.

#### 2.2.1 Normal mode

In normal mode, the CHSC6440 scans the touch screen panel with certain scanning rate, such as the default scanning rate: 60 frames per second.

Users can also speed up or slow down the scanning rate via configuration.

#### 2.2.2 Low-power mode

In low-power mode, the CHSC6440 scans the touch screen panel with a relatively lower rate. The default scanning rate for this mode is 10 frames per second.

Users can also speed up or slow down the scanning rate via configuration.

When in this mode, touch detection is feasible for the CHSC6440, and the chip

DS-CHSC6440 16 Ver 1.2.0

will enter the normal mode if a touch is detected.

#### 2.2.3 Suspend mode

In suspend mode, the CHSC6440 is in standby state and will only respond to external "WAKEUP" signal. Very little current is consumed in this mode, so that the standby time for portable devices can be prolonged.

#### 3 CDSP

The CHSC6440 embeds CDSP and supports up to 40 sensing lines which are configurable. Calculation for accurate touch point coordinate information is implemented via firmware.

The CDSP configures analog front-end parameters, control analog-to-digital conversion and channel switch for flexible scanning time and sensor usage. The collected sampling data from ADC will be stored into internal SRAM and will be translated into accurate touch position information using advanced algorithms.

#### 4 MCU

#### 4.1 Description

The CHSC6440 integrates a powerful 32-bit MCU developed by Chipsemi. The digital core is based on 32-bit RISC, and the length of instructions is 16 bits; four hardware breakpoints are supported.

#### 4.2 Clock

#### 4.2.1 System clock

System clock can be configured through registers.

DS-CHSC6440 17 Ver 1.2.0

#### 4.2.2 ADC clock

ADC clock can be configured through registers.

## 4.3 Reset, Wakeup and Power down enabling

Except for power on reset, it is also feasible to carry out software reset for some modules via registers: if some bit is set to logic "1", corresponding module is reset.

#### 5 Timers

The CHSC6440 supports three timers: Timer0 ~ Timer2. The three timers all support four modes: Mode 0 (System Clock Mode), Mode 1 (GPIO Trigger Mode), Mode 2 (GPIO Pulse Width Mode) and Mode 3 (Tick Mode).

Timer 2 can also be configured as "watchdog" to monitor firmware running.

## 5.1 Mode0 (System Clock Mode)

In Mode 0, system clock is employed as clock source.

After Timer is enabled, Timer Tick (i.e. counting value) is increased by 1 on each positive edge of system clock from preset initial Tick value. Generally the initial Tick value is set to 0.

Once current Timer Tick value matches the preset Timer Capture (i.e. timing value), an interrupt is generated, Tick value is cleared to 0 automatically and Timer status is updated.

## 5.2 Mode1 (GPIO Trigger Mode)

In Mode 1, GPIO is employed as clock source.

After Timer is enabled, Timer Tick (i.e. counting value) is increased by 1 on each positive edge of GPIO from preset initial Tick value. Generally the initial Tick value is set to 0.

DS-CHSC6440 18 Ver 1.2.0

Once current Timer Tick value matches the preset Timer Capture (i.e. timing value), an interrupt is generated and Tick value is cleared to 0 automatically.

## 5.3 Mode2 (GPIO Pulse Width Mode)

In Mode 2, system clock is employed as the unit to measure the width of GPIO pulse.

After Timer is enabled, Timer Tick is triggered by a positive edge of GPIO pulse. Then Timer Tick (i.e. counting value) is increased by 1 on each positive edge of system clock from preset initial Tick value. Generally the initial Tick value is set to 0.

While a negative edge of GPIO pulse is detected, an interrupt is generated. The GPIO pulse width could be calculated in terms of tick count and period of system clock.

#### 5.4 Mode3 (Tick Mode)

In Mode 3, system clock is employed.

After Timer is enabled, Timer Tick starts counting upward, and Timer Tick value is increased by 1 on each positive edge of system clock.

This mode could be used as time indicator. There will be no interrupt generated. Timer Tick keeps rolling loop from 0 to 0xffffffff. When Timer tick overflows, it returns to 0 and starts counting upward again.

#### 5.5 No-wrap mode

When in Mode0 or Mode1, Timer works normally with auto reload feature as described in **section 5.2** or **section 5.3**. In this mode, when Timer tick value reaches preset capture value, an interrupt is generated, and Timer tick value is cleared to 0 automatically. Timer tick value starts rolling from 0 to the capture value again.

DS-CHSC6440 19 Ver 1.2.0

## 5.6 Watchdog

Programmable watchdog could reset chip from unexpected hang up or malfunction.

Only Timer2 supports Watchdog.

#### 6 Interface

The CHSC6440 integrates interfaces as follows:

- ➤ 40 CTP sense pins: S1~S40;

- Configurable pins with multiplexing functions:

- ♦ Up to 4 GPIOs: refer to Table 1-3 of section 1.7

- → I2C: Pin43 SCL -> I2C\_SCL, Pin44 SDA -> I2C\_SDA;

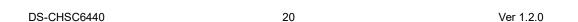

As shown in Figure 6-1, the interface between a host processor and the CHSC6440 consists of I2C interface and an interrupt signal interface. Host gets data and sends "SUSPEND" command to the CHSC6440; while the CHSC6440 reminds Host of reading data.

Figure 6-1 Schematic diagram for interface

DS-CHSC6440 21 Ver 1.2.0

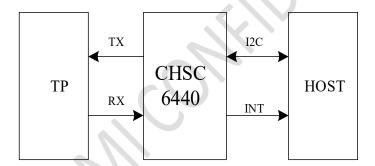

#### 6.1 I2C

I2C module of the CHSC6440 acts as slave. Its related registers are as follows:

Be default, I2C Master can read any internal register and RAM space of the CHSC6440 via I2C.

Figure 6-2 Connection schematic between I2C and AIF\_CTL module

The AIF\_CTL module embedded in the CHSC6440 serves to implement I2C address mapping, and provide cmd register to generate interrupt signal for I2C communication.

#### **6.2 GPIO**

The CHSC6440 supports up to 4 GPIOs.

After GPIO function is enabled for some pin, if the pin is used as output, both "OEN" and "Input Enable" should be cleared, then set "Output" value; if the pin is used as input, both "OEN" and "Input Enable" should be set to logic "1", then set "Input" value.

Drive strength is set as the strongest drive level by default. In actual applications, drive strength can be decreased to lower level if necessary.

DS-CHSC6440 22 Ver 1.2.0

#### 7 Interrupt system

The interrupting function is applied to manage dynamic program sequencing based on real-time events triggered by timers, pins and etc.

The CHSC6440 supports 24 interrupt sources and two priority levels.

When CPU receives an interrupt request (IRQ) from some interrupt source, it will decide whether to respond to the IRQ. If CPU decides to respond, it pauses current routine and starts to execute interrupt service subroutine. Program will jump to certain code address and execute IRQ commands. After finishing interrupt service subroutine, CPU returns to the breakpoint and continues to execute main function.

## 7.1 Enable interrupt sources and priority

Various interrupt sources can be enabled and set as Low Priority via registers.

Any interrupt source could be enabled and set as High priority via registers.

When more than one interrupt sources assert interrupt requests meanwhile, CPU will respond depending on respective interrupt priority level. If there's interrupt source enabled with high priority, CPU should respond to it first.

#### 7.2 Interrupt source indication

Three bytes in register table serve to indicate interrupt sources that have asserted IRQ (Interrupt Request). Once IRQ occurs from certain source, corresponding flag bit will be raised to "High".

#### 7.3 Clear IRQ source

When handling edge-triggered type interrupt, the corresponding IRQ source flag needs to be cleared registers.

As for level-type interrupt, IRQ interrupt source status needs to be cleared via setting corresponding module status register.

DS-CHSC6440 23 Ver 1.2.0

#### 8 Memory configuration

The CHSC6440 embeds 128KB program memory (Flash), 8KB data memory (SRAM) for system use, as well as 2KB SRAM for CDSP use.

#### 9 SAR ADC

The CHSC6440 integrates one SAR ADC module, which can be used to sample CTP module output and internal test point.

#### 9.1 Clock

As for SAR ADC clock configuration, please refer to **Section 4.2.2**ADC clock.

#### 9.2 Resolution

The resolution is selectable via registers.

ADC data format is always 12bits no matter the conversion bit is set. For example, 7 bits conversion will have higher 7 bits as valid bits and the rest bits are to be "1".

#### 9.3 Reference voltage and sampling period

The reference voltage ( $V_{REF}$ ) is selectable via registers: VDDA.

The sampling frequency can be up to 1MHz with operating frequency of 24M for VDD;

Beware of the ADC clock selection and set correct ADC clock divider value. Sampling period is determined by SAR ADC clock period \* (sampling clock cycle + conversion bit + 1).

DS-CHSC6440 24 Ver 1.2.0

## 9.4 Input mode and channel selection

The SAR ADC for the CHSC6440 supports single-end or differential input mode which is selectable via registers.

## 9.6 Reset and power down

ADC\_DATA, ADC\_DATA1 and all SAR ADC configuration registers can be cleared to default value after reset.

## **10 Key Electrical Specifications**

## 10.1 Absolute maximum ratings

Table 10-1 Absolute Maximum Ratings

| Characteristics       | Sym.             | Min. | Max     | Unit | Test Condition |

|-----------------------|------------------|------|---------|------|----------------|

| Supply Voltage        | VDD              | -0.3 | 3.6     | V    |                |

| Voltage on Input Pin  | V                | -0.3 | VDD+0.3 | V    |                |

| voitage on input rin  | V <sub>In</sub>  |      | Max 3.6 | V    |                |

| Output Voltage        | V <sub>Out</sub> | -0.3 | VDD+0.3 | V    |                |

| Output voltage        |                  |      | Max 3.6 |      |                |

| Storage temperature   | T <sub>Str</sub> | -65  | 150     | °C   |                |

| Range                 | • Str            | 03   | 130     |      |                |

| Soldering Temperature | T <sub>Sld</sub> |      | 260     | °C   |                |

**CAUTION:** Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

DS-CHSC6440 25 Ver 1.2.0

## 10.2 Recommended operating condition

Table 10-2 Recommended operation condition

| Item                  | Sym.             | Min | Тур. | Max | Unit | Condition |

|-----------------------|------------------|-----|------|-----|------|-----------|

| Power-supply voltage  | VDD              | 2.6 | 2.8  | 3.6 | V    |           |

| Operating Temperature | T <sub>Opr</sub> | -40 |      | 125 | °C   |           |

| Range                 |                  |     |      |     |      |           |

DS-CHSC6440 26 Ver 1.2.0

## 10.3 DC characteristics

Table 10-3 DC characteristics

| Item              | Sym.              | Min | Тур. | Max | Unit | Condition |

|-------------------|-------------------|-----|------|-----|------|-----------|

| Power Consumption | Idd               |     | 10   |     | mA   |           |

| Suspend Current   | I <sub>Susp</sub> |     | 20   |     | uA   |           |

<sup>\*</sup>Note: All tests above are done at room temperature (T=25°C).

## **10.4 AC characteristics**

Table 10-4 AC Characteristics

| Parameter                                                | Sym.  | Min     | Тур. | Max    | Unit | Condition |  |  |

|----------------------------------------------------------|-------|---------|------|--------|------|-----------|--|--|

| Digital inputs/outputs                                   |       |         |      |        |      |           |  |  |

| Input high voltage                                       | VIH   | 0.7VDD  |      | VDD    | V    |           |  |  |

| Input low voltage                                        | VIL   | VSS     |      | 0.3VDD | V    |           |  |  |

| Output high voltage                                      | VOH   | VDD-0.3 |      | VDD    | V    |           |  |  |

| Output low voltage                                       | VOL   | VSS     |      | 0.3    | V    |           |  |  |

| ADC                                                      |       |         |      |        |      |           |  |  |

| Differential nonlinearity                                | DNL   |         | 0.6  |        | LSB  |           |  |  |

| Integral nonlinearity                                    | INL   |         | 2    |        | LSB  |           |  |  |

| Effective number of bits                                 | ENOB  |         | 10.5 |        | bit  |           |  |  |

|                                                          | SINAD |         | 65   |        | dB   |           |  |  |

| Spurious free dynamic range $(f_{in}=1kHz, f_{s}=16kHz)$ | SFDR  |         | 84   |        | dB   |           |  |  |

DS-CHSC6440 27 Ver 1.2.0

| Parameter           | Sym.             | Min | Тур. | Max | Unit | Condition           |  |  |

|---------------------|------------------|-----|------|-----|------|---------------------|--|--|

| Sampling frequency  | F <sub>S</sub>   |     |      | 2   | MHz  | VDD reference       |  |  |

|                     |                  |     |      | 1   | MHz  | Vbg reference       |  |  |

| 48MHz RC oscillator |                  |     |      |     |      |                     |  |  |

| Nominal frequency   | f <sub>NOM</sub> |     | 48   |     | MHz  |                     |  |  |

| Frequency tolerance | f <sub>TOL</sub> |     | 1    |     | %    | On chip calibration |  |  |

| 32kHz RC oscillator |                  |     |      |     |      |                     |  |  |

| Nominal frequency   | f <sub>NOM</sub> |     | 32   |     | kHz  |                     |  |  |

| Frequency tolerance | f <sub>TOL</sub> |     | 0.5  |     | %    | On chip calibration |  |  |

## 联系方式

# 深圳市中芯微實業有限公司

深圳市龍崗區碧新路2002號中肯大廈607-608

電話/TEL: +86-0755-84200087

www.szzxv.com